━━━ ━━━

半个多世纪以来,硅半导体行业一直在大步前进,压路机般碾过沟坎,公然藐视“燃料将耗尽”“将被竞争者取代”的一再警告。●可以理解,技术人员们不太愿意去预测硅时代的结束。但我们必须作出推测。在过去几十年中,随着硅晶体管物理尺寸的不断缩小,计算机芯片的效率和速度逐步改善,现在开关的微型化对性能改进的作用已不明显。压路机还在前进,但速度已经放缓,而且维护与保养很快也将无法维持。●研究人员们正在寻求多种方案,以确保集成电子工业保持指数级的发展速度。一种可能的方法就是放弃改善硅晶体管,转为改变计算机的体系结构或设计。这一策略曾取得一定成功,例如,由单核处理器转为多核处理器,在系统中集成专用的加速器等等。但可利用的设计技巧有限,而且其中有很多已经用过了。因此,未来的发展仍必须依靠改进底层开关。改变材料和器件尺寸可以制造优于现有硅晶体管电子特性的晶体管。但这种改进方法的收益很小。为了获得更大的进步,只剩下一个选择:完全采用新的纳米技术取代硅。

候选方案有很多种,但到目前为止最令人振奋、最成熟的竞争者是单壁碳纳米管,它是由碳原子连接构成的卷曲片状材料。如果你有似曾相识的感觉,并不奇怪。20世纪90年代,业界对碳纳米管产生了极大的热情,一些大牌的半导体公司开始进行相关研究。但研究人员们在电路制造方面遇到了当时似乎难以克服的困难,对碳纳米管的热情逐渐冷却下来。2004年首次公布石墨烯(平面结构的碳原子晶体)电子特性的测量结果,许多人都急于放弃碳纳米管,而采用这种新技术。

现在碳纳米管又重新回到人们视线中,而且比以往更好用了。与大肆炒作的二维同类产品不同,碳纳米管是天然的半导体,这意味着它可以通过打开和关闭实现二进制开关。最近的材料研究展示已远远超出了逻辑门的演示。例如,2013年,我们在斯坦福大学的研究小组完全依靠碳纳米管电路创建了首款完整的数字系统——一台具有基本功能的计算机。而令人兴奋的是,这台计算机的制造和设计工艺可无缝集成到今天的半导体制造设施中,并可用于制造由数十亿晶体管组成的芯片,能与当前先进的硅进行竞争。

碳纳米管不仅可以强化传统芯片的功能,还可以用于创建全新的计算系统。超速高效三维芯片系统可被用于数据中心,汽车、智能手机等各类移动计算机,或物联网中的传感器。这类3D系统可以结合碳纳米管和新兴存储技术,也可在传统硅电路上直接构建。因此,虽然碳纳米管有可能最终超越硅,但二者也可以共同发展。无论哪种情况,计算能力的巨大进步都将对我们的生活产生深刻影响。

━━━ ━━━

碳纳米管被发现的确切时间很难确定。但很多人以物理学家饭岛澄男发表于1991年的一篇里程碑式的论文为准,他在充气容器中的一个电极上生成了“石墨探针”。饭岛的研究引起了业界的广泛兴趣,很快电气工程师们开始认为碳纳米管可能会是理想的晶体管技术。

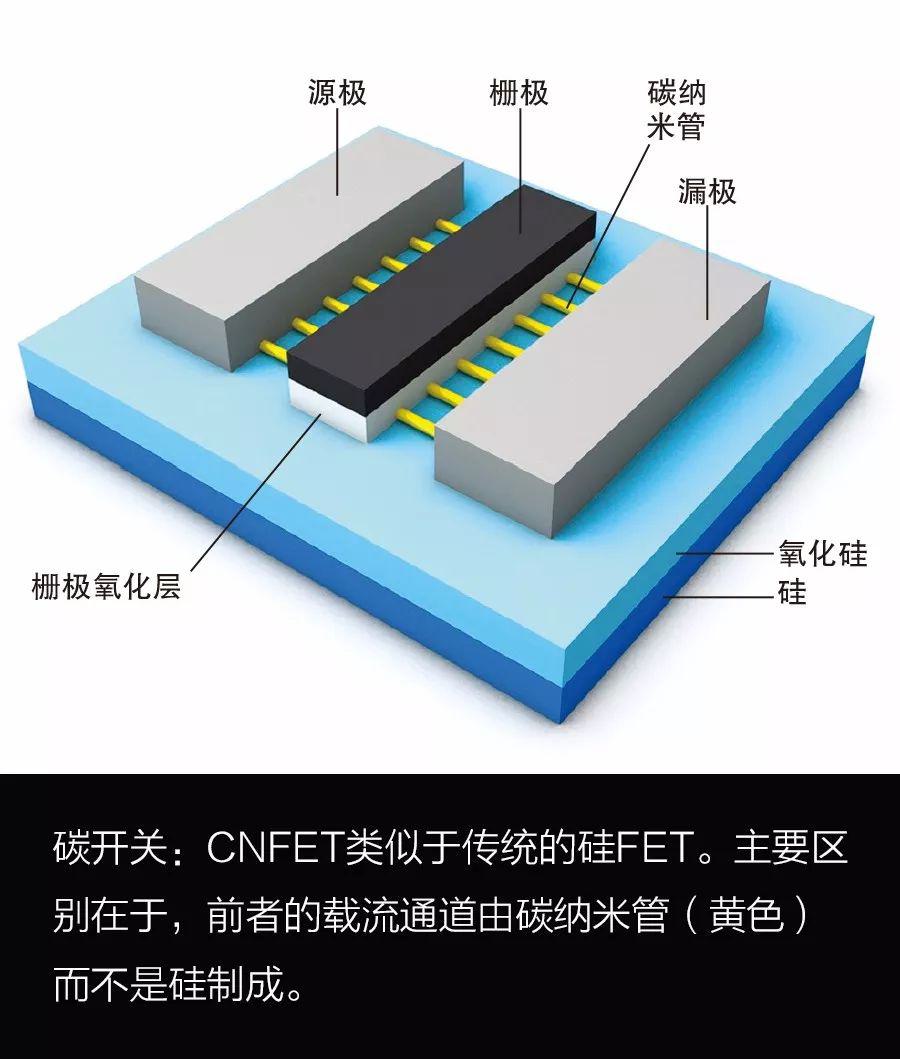

要构建晶体管,需要几个要素:源极和漏极,即电流的起点和终点;两极之间电流流动的通道;通道附近可以控制电流流动的栅极。半导体器件物理结构非常复杂,尤其是今天的纳米级开关,但一般来说,晶体管的性能由两个基本属性决定。首先,沟道流过的电流越大,电路速度越快。这是因为如果电流较大,那么电路中下一个器件的栅极充电速度就会更快。其次,通道越细,器件越节能,因为栅极更容易控制晶体管的开关。如果把通道比作水管,栅极比作你的脚,那么水管越细,阻止水流出来也就越容易。

但可惜,对于今天的超小型硅器件来说,这两个因素(通道的粗细和电荷的流速)存在矛盾。像其他三维块体材料一样,硅越薄,晶体的两侧和边缘对其电特性的影响越强。这种所谓的表面效应会阻碍电荷通过上述材料。

但碳纳米管自身同时满足了晶体管通道这两方面的要求。纳米管壁光滑,本身没有悬空键,电荷流速很快,比硅快很多倍。而且由于碳纳米管也非常细(直径大约1纳米左右),栅极可轻易控制其中的电流。

碳纳米管晶体管看上去与硅晶体管大致相同。主要区别在于通道材料是碳纳米管,而不是硅。就像硅晶体管一样,栅极产生的电场控制电流;又像硅芯片一样,可利用芯片附加层中内置的微金属导线连接碳纳米管晶体管形成电路。

1998年,荷兰代尔夫特理工大学和IBM的两个独立研究小组宣布首次制造出碳纳米管场效应晶体管(CNFET)。在随后的几年中,研究人员们设计了一系列实验来研究这些器件的基本物理特性。他们也开始构建基本电路;2006年取得显著突破,IBM研究小组利用一根18微米长的碳纳米管构建了12个CNFET,制成环形振荡器(重要的逻辑演示电路)。

取得的成就虽然举世瞩目,但由单一碳纳米管创建的小型测试电路与最先进的硅芯片之间尚有很大差距。为了制造芯片,研究人员要找到一种利用大量碳纳米管构建数以亿计晶体管的方法。对于高性能电路的一些要求很早就被提出。为了驱动足够的电荷与硅电路的速度一较高下,每个晶体管沟道需要包含多个密集碳纳米管。此外,这些密集碳纳米管的间隔应均匀,减少晶体管之间的电特性变化。

要达到这一密度和一致性水平,可在紧密排列的碳纳米管整齐的阵列上创建晶体管的源极、漏极和栅极。但可以想象,在硅衬底上整齐排列数十亿相同的卷曲式碳片并不容易。

问题首先是碳纳米管的合成。生成碳纳米管的过程几乎不可避免地会产生具有不同直径和原子排列方式的纳米管。底层原子结构的变化会产生具有不同电特性的碳纳米管。有些具有半导体特性,而另一些具有金属特性。半导体性碳纳米管适用于数字逻辑,正是我们想要的,而栅极无法关闭金属性碳纳米管,因此基本上只能作为导线。所以,即使在应关闭晶体管的情况下,金属性的碳纳米管也总是会传导电流,浪费功率,并会导致逻辑操作错误。

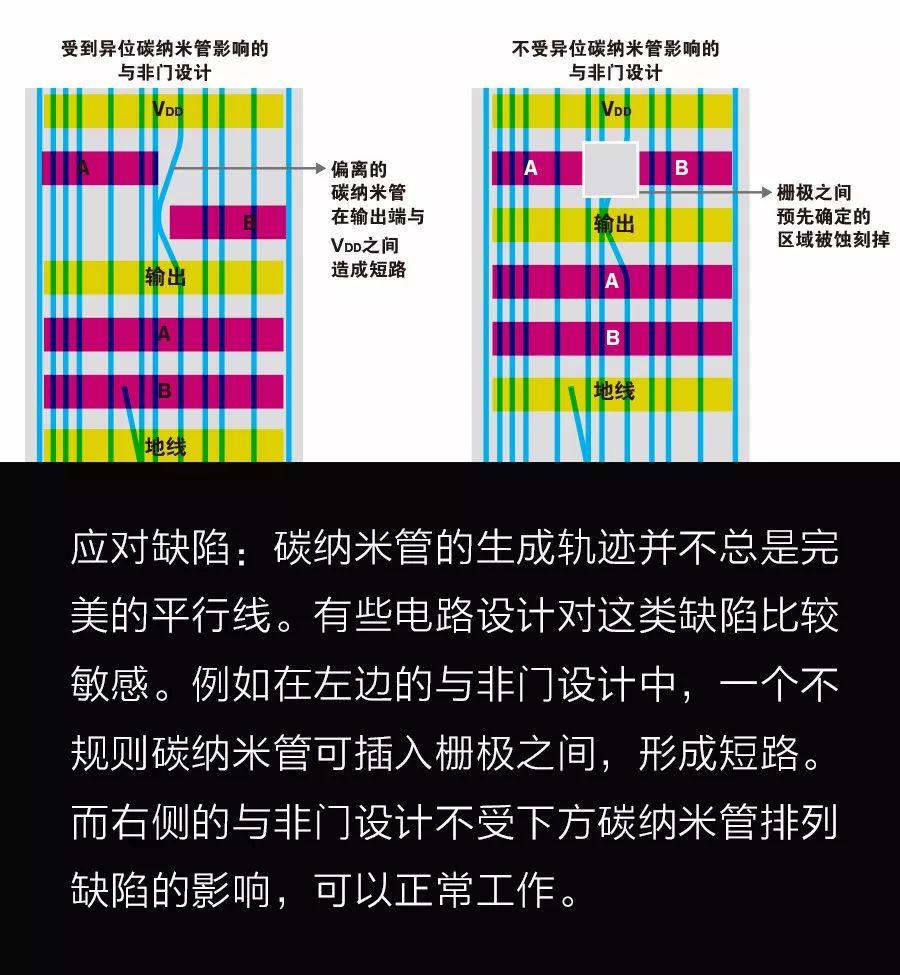

更糟糕的是,很难在表面上实现完全平整的碳纳米管阵列。如果其中一些碳纳米管方向杂乱,可能会超出自身晶体管沟道的局限,形成随机电路连接。在不同的点,纳米管的密度也不相同,会导致晶体管的载流能力差异很大。而一些晶体管沟道中很可能没有碳纳米管,从而导致器件失效。

━━━ ━━━

2004年,斯坦福大学的两位教授(即本文作者Subhasish Mitra和黄汉森)带领一群学生和博士后开始着手解决这些问题。本文另一位作者(Max Shulaker)从2009年开始作为一名本科生加入该组工作,他很快将到麻省理工学院任教。我们开展工作时,碳纳米管的研究领域已大大萎缩。但是,我们希望与其他规模小但具有创新精神的研究团队一道,找到将纳米材料从实验室的研究物转变成芯片材料的方法。

首先,我们侧重于解决前面提到的高性能电路的两个主要障碍:碳纳米管排列不整齐以及金属纳米管的问题。第一步是要找到生成排列尽可能一致的碳纳米管的方法。受到伊利诺伊大学厄巴纳-香槟分校和南加州大学所开展工作的启发,我们选定的方法是在结晶石英衬底上生成碳纳米管。

当被富碳气体包围时,石英晶片表面粘附的金属纳米粒子会以完美有序的方式生成平行的碳纳米管。而后通过在碳纳米管涂上金属薄层,可将碳纳米管转移到传统的芯片基板(硅上面的绝缘二氧化硅层)上。金属在这里充当粘合剂,而后可以将其从石英上剥离,并转移到硅上。然后用化学方法将金属层蚀刻掉,留下排布精密的碳纳米管阵列。(企业已利用类似的转移工艺来制造传统芯片的绝缘硅晶片。)

但我们发现,即使有石英作为导引物,仍有较小比例的碳纳米管(约0.5%)无法正常生成。它们最开始是沿直线生成,不料会出现偏转,最后成为斜线。为了解决纳米管不一致问题,我们想出了有效设计碳纳米管周围电路的办法。基于图论的自动化设计算法能够决定应蚀刻掉电路的哪些部分,因此从数学上讲不会有异位的纳米管连接到不应连接的两个电极。这种处理可以确保不一致的碳纳米管不会造成逻辑错误的短路。重要的是,这个过程无须了解异位碳纳米管的确切位置,相同的设计适用于任何启动配置。如果没有这种策略,我们就需要检查每个晶片和每个碳纳米管,以找到异位纳米管,这个过程不现实,而且代价很高。

我们发现,可以结合类似的处理和设计来解决金属纳米管问题。2001年,IBM研究小组发现,如施加足够的电压,就可通过焚烧来消除金属碳纳米管。我们采用了这种技术,通过建立临时线路,有效地把整个芯片变为一个巨型的晶体管,同时在整个集成电路上进行操作。电路创建后,我们在晶体管的栅极施加了一个电压,关闭所有半导体碳纳米管。然后在每个源区和漏区施加一个电压。因为半导体碳纳米管已经关闭,只有沟道中的金属纳米管可以导电。如有足够强的电压脉冲,即便这些金属纳米管的电阻很低,也会产生烧坏纳米管的瞬间热量,将其转变为少量的二氧化碳。今天,我们使用了这种方法的一种变型,可以将一根金属性纳米管全部消除,并且对所有金属性纳米管的消除率高达99.99%。在这个过程中,也会牺牲一小部分半导体碳纳米管,但在可控的范围内(不到1%)。

因解决了杂乱碳纳米管及金属性纳米管的问题,所以只需实用化、规模化的生产方式就可利用碳纳米管构建出第一批数字系统(我们将这种加工和设计的结合称为“零缺陷范式”)。首次验证这一系统的是萨沙(Sacha),它是我们于2013年在旧金山召开的IEEE国际固态电路会议上展示的一款握手机器人。当机器人的手被抓住时,碳纳米管子系统会感知到嵌入式电容传感器数值的变化,并触发机器人握手。虽然不可否认这个演示有些简单,但萨沙的确说明了很重要的一点:CNFET已经达到成熟水平,可以进行系统级的现场示范。

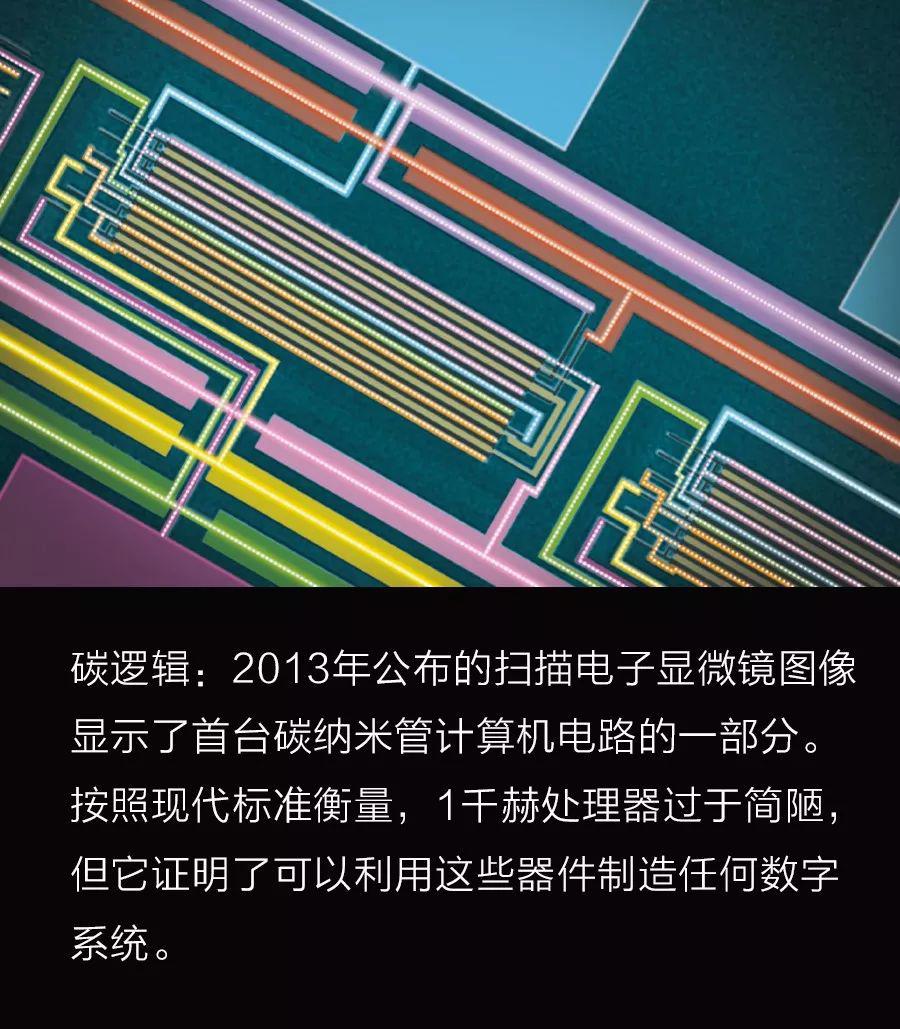

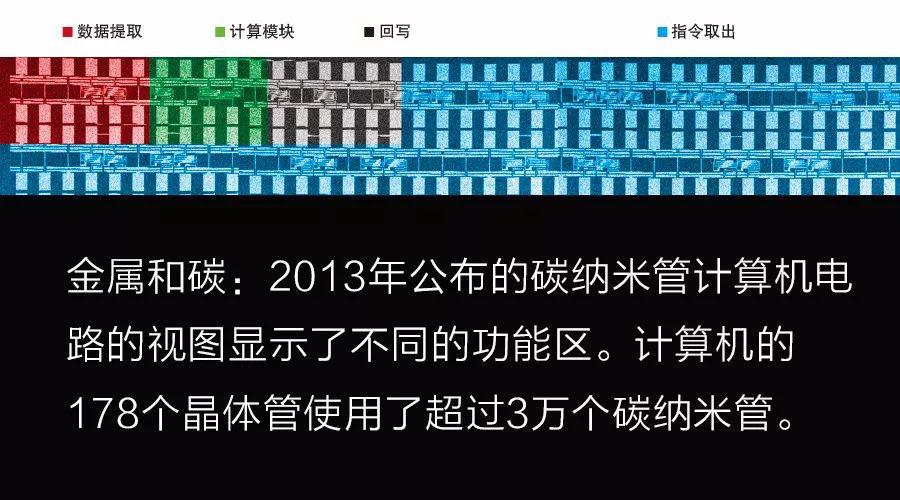

为了充分说明碳纳米管电路的可行性,我们还创建了一个完整的数字系统:首台完全依靠CNFET制造的计算机处理器。处理器仅由178个包含3万多个碳纳米管的CNFET制造而成,这按照现代标准来说并不多。该系统使用1位结构,时钟频率为1千赫,不到现在CPU时钟速度的百万分之一。但我们没有进行速度优化,芯片之所以慢,部分原因是我们在每个节点都安装了探测器,以监控计算机内部每一次可能的转换。尽管如此,这台处理器仍是完整的计算机;它可以执行多项任务,模拟商业MIPS指令集的指令。更重要的是,它表明CNFET可用来创建任何类型的数字系统,是今天不断涌现的纳米技术的成功先例。

━━━ ━━━

当然,仅靠整合不可能产生什么尖端技术。CNFET电路的性能仍远落后于硅。其中核心挑战就是碳纳米管的密度问题。2013年我们宣布制造出碳纳米管计算机时,能够在晶体管沟道的垂直线上生成线性密度为每微米1至10个碳毫微管的碳纳米管阵列。为了确保高性能CNFET具备充分的载流能力,需要将以上数值提高10至100倍,还需要确保每个点的密度都是统一的,以便将晶体管偏差保持在最低的水平。

2014年,我们宣布开发了一种能够同时应对这些挑战的新技术。该方法基于之前将碳纳米管从石英衬底移到芯片基板上的策略。我们发现,这种方法可反复使用,将一个碳纳米管阵列层叠到另一个阵列上。因为通常情况下,稀疏的均匀阵列更容易实现,利用这种多次转移方法也可将密度问题与均匀度问题分解开来。也就是说,可以制备多个稀疏阵列,然后进行层叠,从而提高密度。

不同于其他潜在的纳米电子器件,我们用这种方法制成的CNFET的载流能力差不多与同等大小的硅晶体管持平。这对碳纳米技术而言是史无前例的性能,预计CNFET将有更大的提升空间。

我们的方法并不是制造碳纳米管电路的唯一方法。例如,IBM等几家公司的研究团队研究了在溶液中保持悬浮状态的半导体和金属纳米管。金属纳米管被分离并除去。然后剩余碳纳米管可以按照特定位置和方向,落在刻有图案的基底上进行干燥。研究人员们仍在努力减少残留的金属纳米管,提高半导体纳米管的密度,这种方法前景非常乐观。

尽管取得了上述进步,但在涉及碳纳米管计算时,我们还是遭到了质疑。其中一个经常被提及的问题是可否创建互补逻辑。今天的处理器使用CMOS半导体技术,其中文名称为“互补金属氧化物半导体”,“互补”是指它采用两种不同类型的晶体管:携带电子的n型晶体管和使用空穴(没有电子的正电荷)的p型晶体管。使用两种类型有许多优点,但多年来研究人员们基本上只研究p型碳纳米管晶体管。这是因为首个CNFET是p型晶体管,所用的材料处理起来更容易。的确,我们的碳纳米管计算机完全由p型CNFET制造。

但碳纳米管本质上没有什么类型之别,完全可以将其掺杂起来以承载任何一种电荷载子。这种掺杂可通过选择栅极与沟道之间或晶体管金属源极与漏区之间的绝缘层材料实现,而不是像硅材料那样在材料中插入其他类型的原子。在“源”和“漏”的情况下,这些材料基本上充当过滤器,使电子或空穴进入碳纳米管沟道。许多研究小组(包括我们的研究小组)都采用这些方法来创建n型和p型CNFET。此外,我们已经证明,这两种类型器件的性能不相上下,这是设计电路时需要着重考虑的一个因素。

另一个问题是碳纳米管与金属源极和漏极触点之间的电连接。如果这些电连接不完美,那么电阻就较高,能耗高,计算缓慢。但随着晶体管的尺寸变得越来越小,这会成为困扰所有晶体管的问题。很难根据原子尺度对材料进行配对。所幸对于碳纳米管晶体管而言,要实现高性能的CNFET电路并不需要非常完美的电接触。此外,IBM最近的研究表明,可以通过熔合两种材料,形成从碳到金属的近无缝过渡,使碳纳米管与其金属触点之间的连接有较大改进。

如果希望这些芯片能够与硅一较高下,必须把所有这些碳纳米管器件的制造方式结合起来,包括掺杂和触点结构制备。进一步降低变异性也要优先解决,因为限制芯片性能的不是其中最好的晶体管,而是最差的晶体管。这些都是巨大的挑战,但一旦克服这些挑战也会带来巨大的回报。根据实验数据校准的模型显示,即使会有变异和其他缺陷,用碳纳米管制造的微处理器的能量-延时积(EDP,一种电路速度和能源效率的衡量标准)也是硅电路的10倍。随着晶体管体积不断缩小,其优势会更加明显,因为硅设备会在碳纳米管器件之前达到尺寸极限。

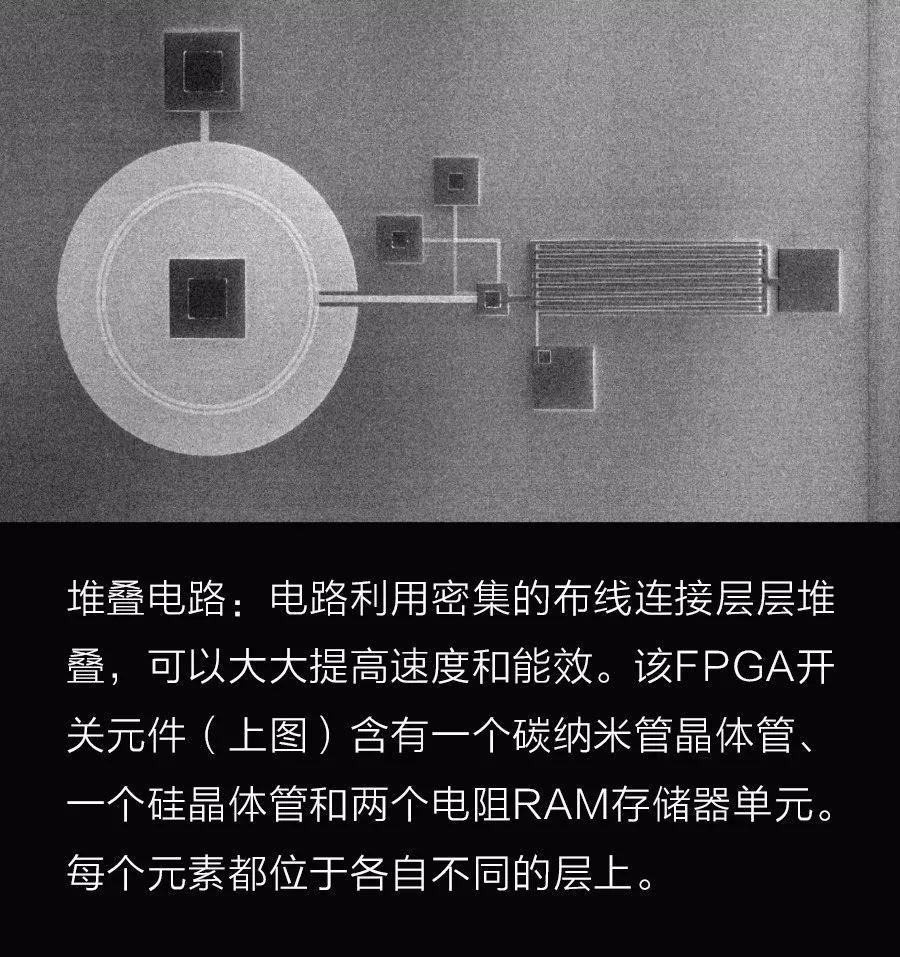

碳纳米管还有其他优点。芯片设计的一个新兴领域是3D单片集成,形成直接在彼此上堆叠、通过大量的超细垂直导线相连的高层电路。

之所以形成这种结构是有原因的。当今的计算机花费大量的时间和能量在处理器内以及处理器与片外存储器之间的几毫米或几厘米的空间中传送数据。现在可以通过制造单独的2D硅芯片,然后将其堆叠捆绑在一起,创建结合逻辑和内存的3D芯片。各层通过非常大而稀疏的垂直导线连接。如果3D结构的连接密集,就会突破现在逻辑与内存之间存在的障碍,这对处理大量数据的应用程序将大有裨益。

这种单片3D集成在硅中很难实现;制造晶体管的温度通常很高,可能会使金属导线熔化,破坏下面的晶体管。但利用前面描述的碳纳米管转移技术,就可在不破坏底层电路的温度下创建电路。这是因为这种方法基本上可以将材料的高温生成阶段(约900摄氏度)与其余的电路制造工艺步骤分离开来。这不是推测;我们已经展示了几款可操作的CNFET单片3D集成电路。这项工艺可与硅兼容,甚至可以用来在硅晶体管的基础上添加碳纳米管器件层。

预测显示,在3D系统中结合碳纳米管晶体管和新兴存储设备所产生的能源效率可能会比带有片外存储器的传统硅芯片高100到1000倍(这个估计假定两种芯片的特征尺寸相近)。

当然,随着碳纳米管研究不断推进,其他研究也会研制出更好的晶体管。例如有一种较新的方法,负电容FET,它利用栅极与沟道之间的材料来提高栅极电压的影响,减少开关所需要的能量。这种设计可与碳纳米管兼容,具有更大的优势。其他替代技术也在研究之中,如利用电子隧穿和控制电子旋转的晶体管。但CNFET仍是唯一在性能、显示系统复杂性和制造成熟度方面都达到高水平的新兴纳米技术。

那么这种碳纳米管电路何时可用于智能手机和数据中心呢?像其他新技术一样,只有当芯片制造商真的决定生产时,碳纳米管才能融合到计算技术高速公路中。由于最近碳纳米管制造和设计的进步,再加上这种材料实际上可以作为硅的补充,我们离这个目标越来越近了。只要我们愿意再加把劲儿,它就能超越硅。

作者: Max Shulaker

往期推荐