本文主要介绍RF天线的阻抗调试过程。

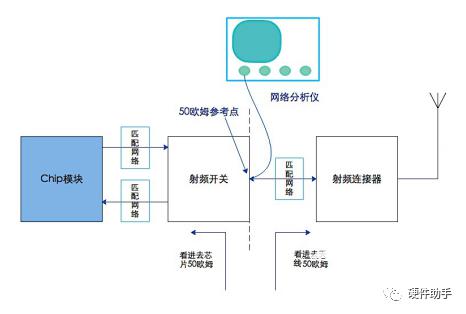

校准网络分析仪;

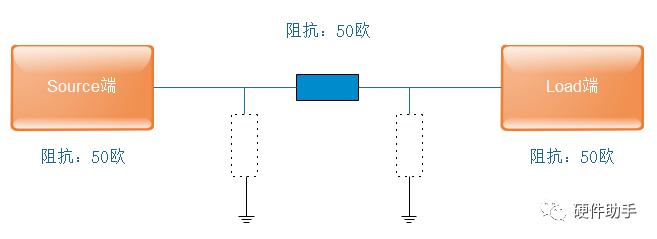

通过网络分析仪测量阻抗;

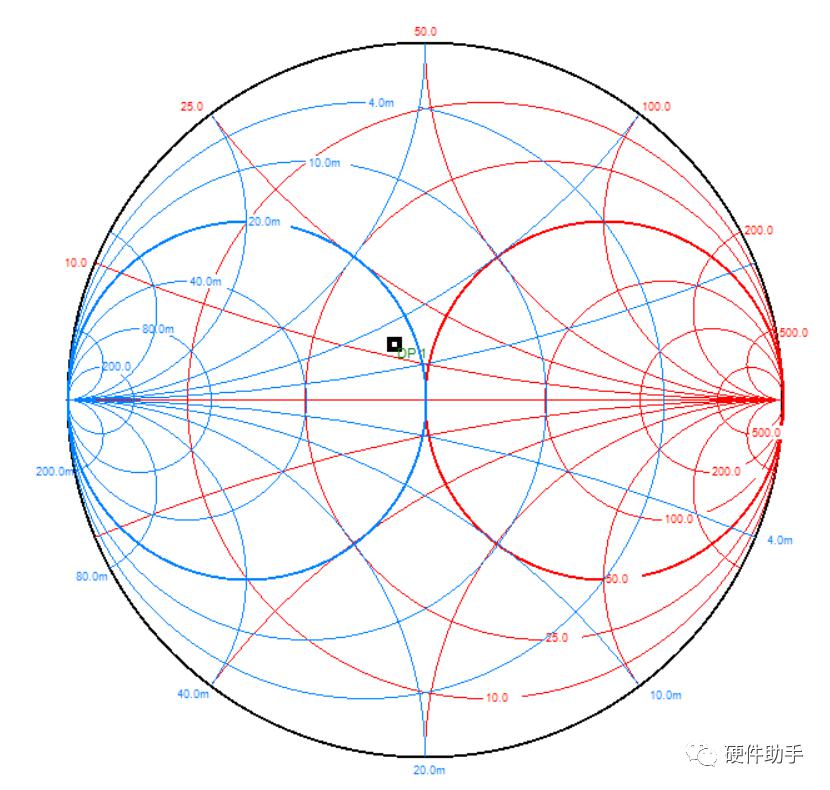

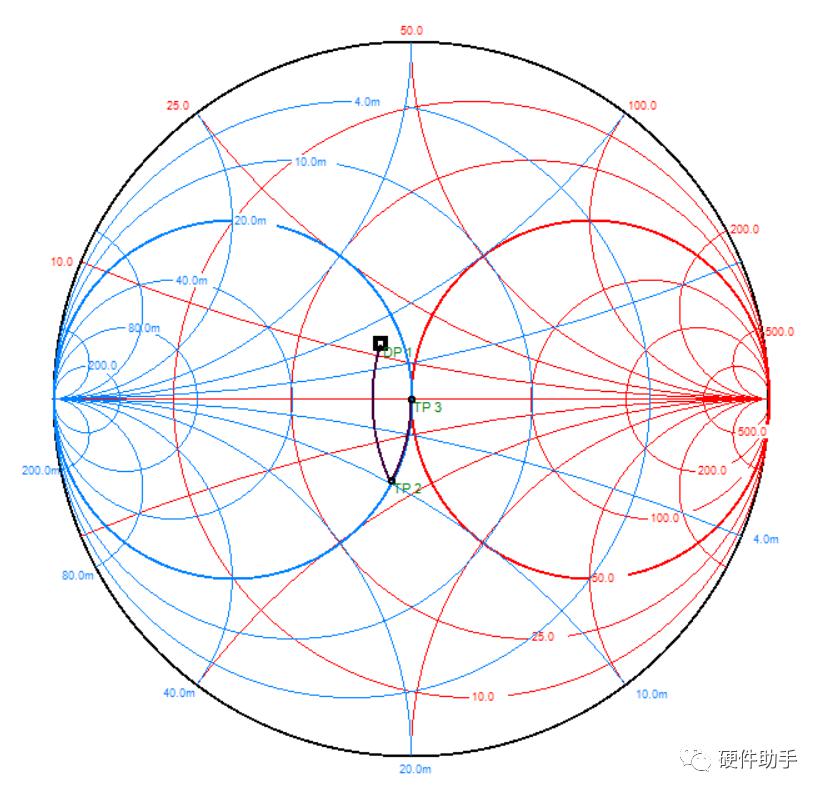

借助史密斯圆图进行阻抗匹配;

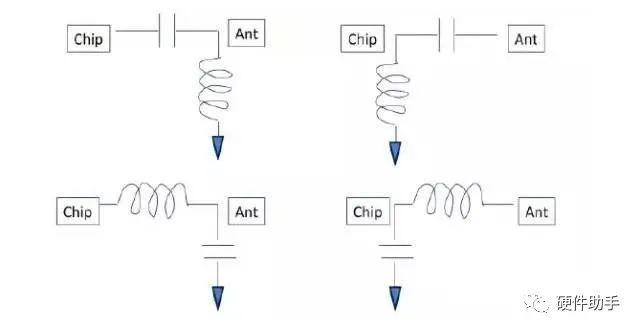

选择合适的电容和电感焊接到PCB上;

测量无线芯片的输出和输入是否满足要求。

落地电容值不要过大,电容越大,容抗则越小,信号容易流入GND。

电容、电感值不要过小,因为存在误差,容值、感值越小,误差影响越大,影响批次的稳定性。

电容、电感选择常规值,方便替换和备料采购。没有完全匹配的就要选择相接近的参数值。把所匹配到器件值上到对应的位置,需要用矢量网络分析仪再次去验证,根据实际结果,再次进行器件值微调。

以上就是针对射频天线阻抗的大致调试流程。